# Embedded real-time system for motion and deformation measurement

Seyfeddine BOUKHTACHE

Institut Pascal : ISPR

#### Introduction

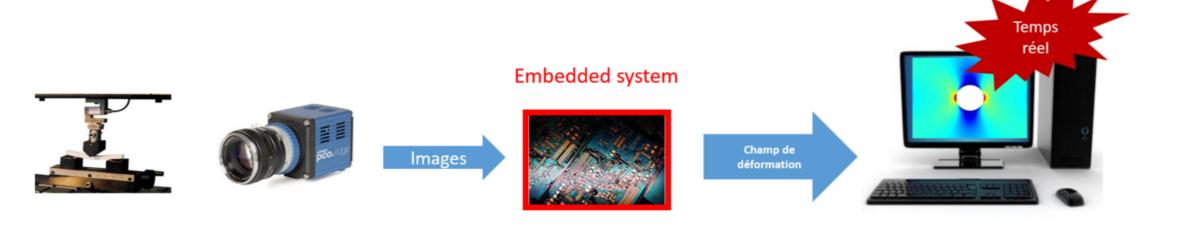

- ▶ Digital image correlation (DIC) is a popular and efficient technique for motion and deformation measurements as it provides sub-pixel accuracy. But it represents a significant drawback, extremely huge computational (iterative algorithm, ...).

- ► The current solution consists on off-line processing

Figure 1: Current solution

#### **Objectives**

► Field-Programmable Gate Array (FPGA) for real-time: parallelism, pipeline

Figure 2: smart camera

- 1. Real-time

- 2. Achieve high-accuracy  $(10^{-3})$

- 3. Optimal architecture (Logic, DSP, memory, area and operating frequency)

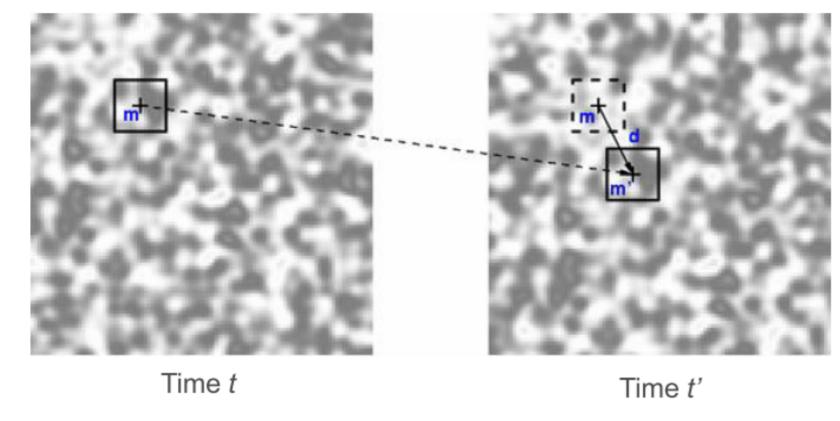

## DIC principle

- ► Track each image pixel by comparing gray level values of the images taken before and after deformation.

- ► Many pixels in the deformed image may have the same gray level value, hence neighboring pixels are used.

Figure 3: Subset Tracking

▶ DIC is based on minimizing the gray value difference between a reference subset and deformed subset [1].

$$U(X_0) = argmin \sum_{Rol} [f(X_0) - g(X_0 + U(X_0))]^2 dX_0$$

(1)

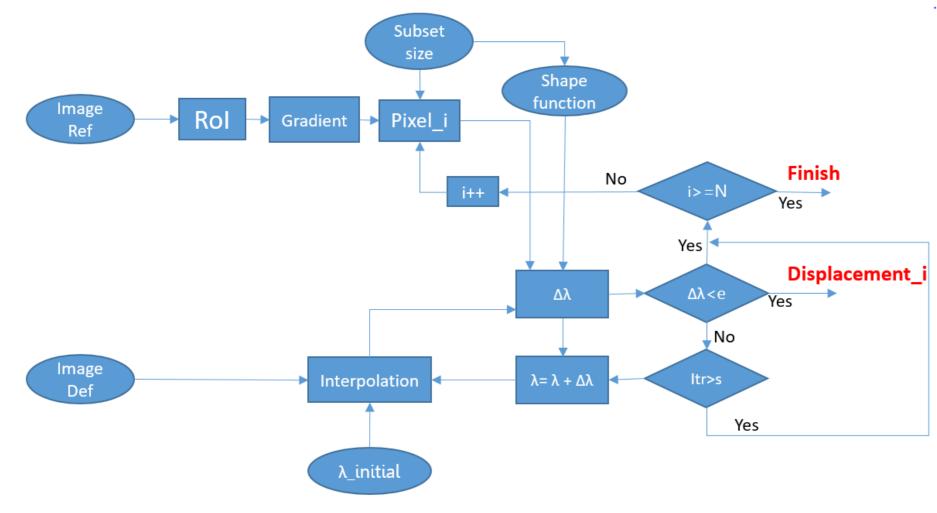

# Algorithm

Figure 4: DIC algorithm

## Interpolation

| Method                             | Bi-linear | Bi-cubic | B-spline               |

|------------------------------------|-----------|----------|------------------------|

| Complexity                         | Low       | Complex  | Difficult to implement |

| Accuracy                           | Low       | High     | Excellent              |

| Table 1: Interpolation methods [2] |           |          |                        |

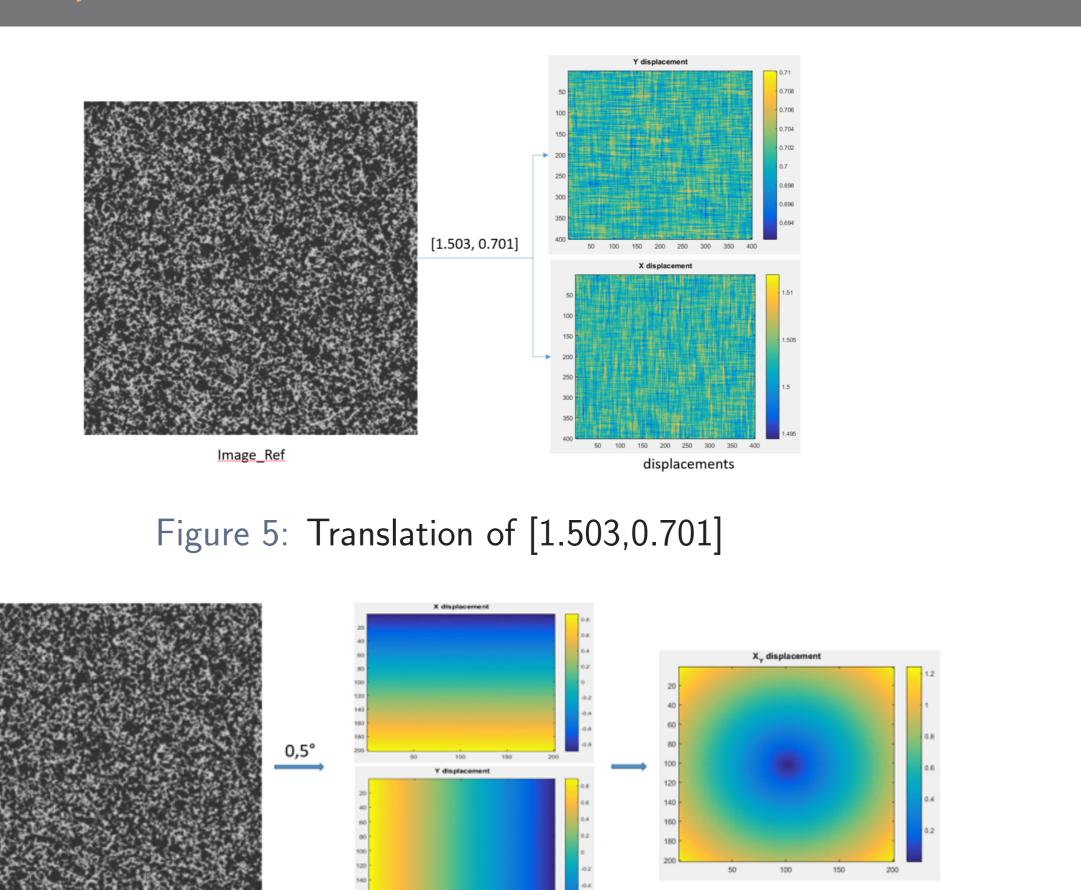

#### Results (Matlab)

Figure 6: Rotation of 0.5°

X and Y displacements

X Y displacements

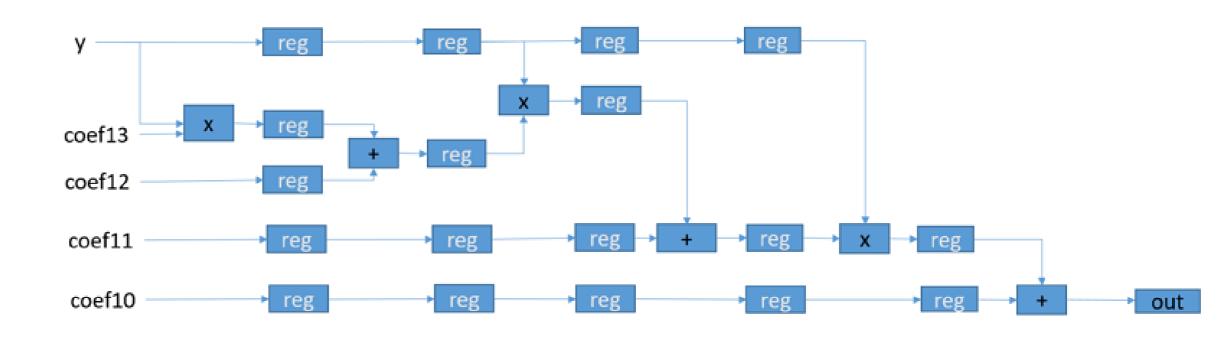

#### Implementaion of Bi-cubic interpolation

- ► Hardware architecture

- ▶ Mathematic reformulation

- Avoiding redundant computations

- Coefficients block

- ► 5 bi-cubic sub-block

Figure 7: Bi-cubic sub-block

► The algorithm is coded in VHDL and implemented into FPGA Cyclone V Image size Frequency max DSP(18x18) Logic (ALMs) Memory (bits) 1024x1024 204 MHz 15 (17%) 1786 (6%) 30657 (< 1%)

Table 2: Resources utilization report

# Conclusion and perspectives

- ▶ Bi-cubic interpolation is selected because it represents the best trade-off between complexity and accuracy. Our proposed architecture improves the operating frequency [3] and it is well suited for practical real-time applications such as DIC.

- ► As a perspective, the implementation of DIC based on bi-cubic interpolation is envisaged.

#### References

- [1] Michael A. Sutton, Jean-Jos Orteu and Hubert W. Schreier. "Image Correlation for Shape, Motion and Deformation Measurements". Springer, 2009

- [2] Han, D. "Comparison of Commonly Used Image Interpolation Methods". 2nd International Conference on Computer Science and Electronics Engineering (ICCSEE 2013), (Iccsee), 15561559.

- [3] G.Mahale, H.Mahale, R.B.Parimi, S.K.Nandy, S.Bhattacharya. "Hardware Architecture of Bi-Cubic Convolution Interpolation for Real-time Image Scaling". International Conference on Field-Programmable Technology (FPT) 2014.

### **Contact Information**

► Email: seyfeddine.boukhtache@uca.fr